Chip发表南京邮电大学蔡志匡团队综述:针对芯粒互连的故障建模、测试与修复

- 2026-04-25 07:08:23

FUTURE | 远见 Chip编辑部

近日,南京邮电大学蔡志匡团队以「Fault modeling, testing, and repair for chiplet interconnects」1为题在Chip上发表长篇综述论文,文章针对集成芯片的互连测试难题,深入探讨了故障建模、TSV/ILV测试及冗余修复策略,通过多维度的测试方法与动态修复手段,确保了芯粒互连的高可靠性。第一作者为刘小婷,通讯作者为蔡志匡。

随着半导体技术的不断进步,芯粒技术因其在提升性能、降低功耗和节省空间方面的显著优势而日益受到重视2。然而,3D集成电路中的垂直互连结构,如通孔硅通孔和层间通孔,在建模、测试和修复方面带来了前所未有的挑战3。本文围绕四个模块展开:故障建模、TSV(Through silicon via)测试、ILV(Inter-layer via)测试以及修复策略。

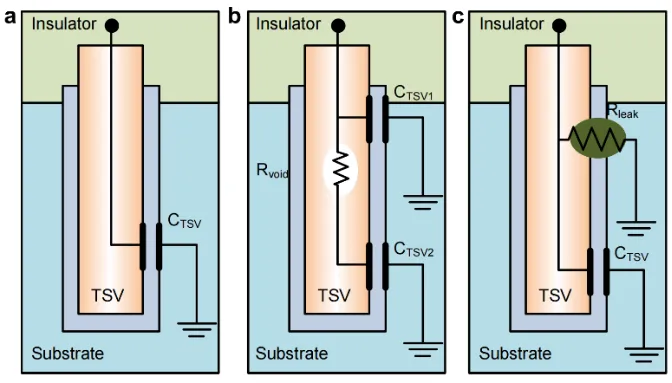

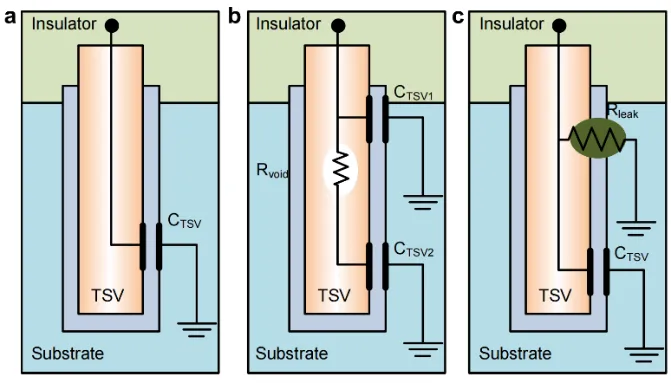

首先,文章介绍了建立TSV故障模型的不同方法,并讨论了不同缺陷对性能的影响。随后,分析了检测TSV各种故障(如短路、延迟故障和串扰)所面临的挑战,以及相应提出的测试方法。同时,文中还讨论了一些电参数测试方法。

图1TSV故障模型。a,无故障;b,空洞故障;c,泄漏故障。4

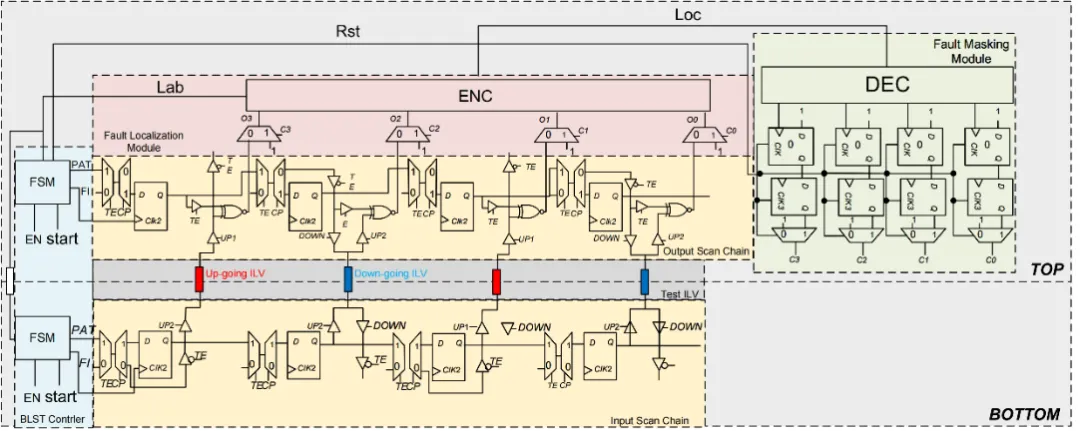

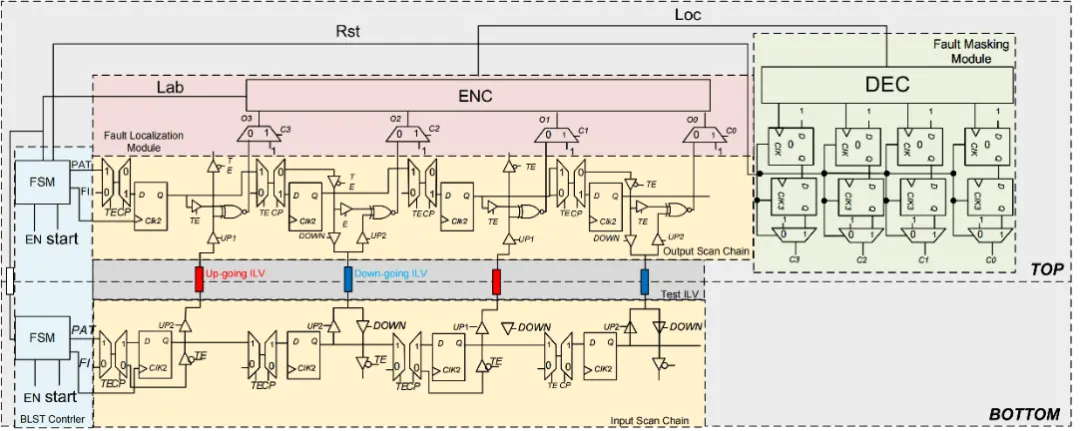

在ILV测试技术方面,文章讨论了由于ILV尺寸小、密度高而导致传统测试方法难以奏效的问题,并探讨了多种测试与优化方法,旨在在尽量减少测试时间和硬件开销的同时,提高故障覆盖率。

图2基于扫描链的ILV内建自测试架构。5

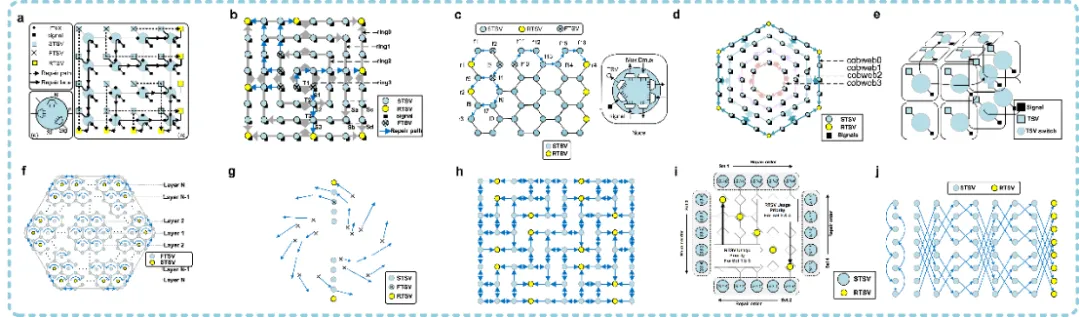

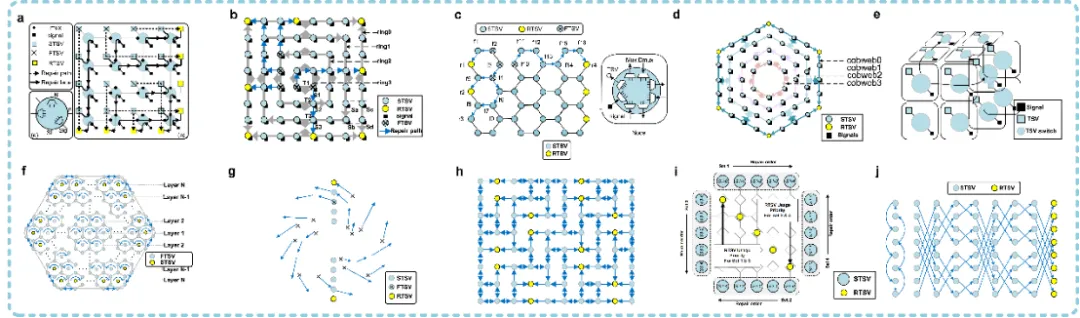

此外,本文还分析了基于冗余TSV的修复策略,介绍了包括环形结构、蜂窝结构等在内的冗余修复架构。与此同时,文章还探讨了动态实时故障修复方法,例如时分多址和在线修复技术,这些方法旨在提升3D IC的可靠性和使用寿命。

图3具有代表性的修复架构。

本文为集成芯片测试构建了一套全流程的保障体系,该体系首先通过对互连进行精准故障建模,剖析各类缺陷对系统性能的深层影响。在此基础上,探讨兼顾高覆盖率与低硬件开销的高效测试方法。最后,依托冗余TSV架构及TDMA、在线修复等动态技术,实现对故障冗余替换,从而全方位提升集成芯片的可靠性。

Fault modeling, testing, and repair for chiplet interconnects¹

With the continuous advancement of semiconductor technology, chiplet technology has gained importance due to its significant advantages in enhancing performance, reducing power consumption, and saving space.2However, vertical interconnect structures in 3D integrated circuits, such as through-silicon via and inter-layer via, present unprecedented challenges in modeling, testing, and repair.3This paper focuses on four modules: modeling for faults, TSV testing, ILV testing, and repair strategies.

First, different methods of establishing TSV fault models and discussions on the influence of different defects on performance are introduced. Then, the challenges in detecting various faults of TSVs, such as short, delay faults, and crosstalk, and the presented corresponding testing methods are analyzed. Meanwhile, some electric parameter test methods are also discussed.

Fig. 1Fault model of TSVs. a, Fault-free, b, void fault, c, leakage fault.4

In the ILV testing technology, the difficulties caused by the small size and high density of ILVs, which make traditional testing methods less effective, are discussed. Various testing and optimization methods are explored, aimed at improving fault coverage while minimizing testing time and hardware overhead. Moreover, repair strategies based on redundant TSVs are analyzed in this paper. Redundant repair architectures, including ring-based, honeycomb, and so on, are introduced.

Fig. 2Scan-chain-based ILV-BIST architecture.5

Additionally, the paper explores dynamic real-time fault-repair methods, such as time-division multiple access and online repair technologies, which aim to enhance the reliability and lifespan of 3D ICs.

Fig. 3Representative repair architectures.

This paper establishes a comprehensive assurance framework for integrated chip testing. The framework begins with precise fault modeling of interconnects to analyze the profound impact of various defects on system performance. On this basis, it explores efficient testing methodologies that balance high fault coverage with minimal hardware overhead. Finally, by leveraging redundant TSV architectures and dynamic mechanisms such as TDMA and online repair, the framework enables effective fault replacement, thereby providing an end-to-end enhancement for the reliability of integrated chips.

参考文献

1. Liu, X. et al. Fault modeling, testing, and repair for chiplet interconnects. Chip5, 100160 (2026).

2. Van der Plas, G. et al. Design issues and considerations for low-cost 3-D TSV IC technology. IEEE J. Solid-State Circuits46, 293e307 (2011).

3. Cho, D. H. et al. A review on the fabrication and reliability of three-dimensional integration technologies for microelectronic packaging: through-Si-via and solder bumping process. Metals11, 1664 (2021).

4. Hao, C. et al. Pulse shrinkage based pre-bond through silicon vias test in 3D-IC. In 2015 IEEE 33rd VLSI Test Symposium (VTS), 1-6 (IEEE, 2015).

5. Chen, T. et al. A scan-chain based built-in self-test for ILV in monolithic 3D ICs. IEEE Trans. Instrum. Meas. 73, 1-13 (2024).

论文链接:https://doi.org/10.1016/j.chip.2025.100160

扫码阅读原文

作者简介

刘小婷,南京邮电大学博士研究生,主要方向主要为芯粒互连测试技术与优化算法研究。

Xiaoting Liu is a PhD student at Nanjing University of Posts and Telecommunications. Her research primarily focuses on chiplet interconnect testing technology and optimization algorithms.

蔡志匡,南京邮电大学教授、博士生导师。长期致力于芯粒测试、测试大模型及测试机专用芯片等前沿领域的研究工作。先后主持国家重点研发计划、国家自然科学基金重点项目等各类科研项目20余项;在国内外权威期刊及会议发表高水平学术论文120余篇。

Zhikuang Cai, Professor and PhD Supervisor at Nanjing University of Posts and Telecommunications. He is dedicated to research in Chiplet testing, testing-oriented LLMs, and ATE-specific chip design. With a portfolio of 20+ major research projects—notably the National Key R&D Program and NSFC Key Programs—his work has significantly advanced the field. He has authored over 120 peer-reviewed publications in top-tier journals and conferences.

关于Chip

Chip(ISSN:2772-2724,CN:31-2189/O4)是全球唯一聚焦芯片类研究的综合性国际期刊,已入选由中国科协、教育部、科技部、中科院等单位联合实施的「中国科技期刊卓越行动计划高起点新刊项目」、「中国科技期刊卓越行动计划二期项目-英文梯队期刊」,为科技部鼓励发表「三类高质量论文」期刊之一。

爱思唯尔Chip官网:

End